# 小型ジャイロシステムの開発

小磯賢智\*,水谷誠司\*

## Development of Small Gyroscope System

## Kenchi KOISO and Seiji MIZUTANI

## 1. はじめに

ジャイロセンサーは、近年勢いを増して急速に利用が拡大している。その背景としては、一般家庭用ゲーム機や携帯電話をはじめ、デジタル・スチルカメラなどの家電製品や車載ナビゲーションシステムなど、身近にある機器に搭載されていることが挙げられる。携帯ゲーム機器や携帯情報端末が小型になり使い勝手がよくなるにつれ内蔵されるセンサーについても、より小型で省電力、高性能化が求められ開発競争は激しくなる一方である<sup>1)</sup>.

これまで, 二次元振動型ジャイロ装置に関して, その構造や動作メカニズム, 動体検出法について詳 述してきた. とくに、この研究で開発されたデジタ ル処理による位相差検出法 2),3)については,これまで のアナログ出力からデジタル値を求めるいわゆる A/D 変換方式とは全く異なり、きわめて正確な水晶 発振を用いて高精度な動体検出が可能であることを 示した. また, ジャイロ本体の動作についても, 駆 動回路モデルの構築からシミュレーションの動作波 形の検証を比較することで正常な応答範囲であるこ とがわかった 4). この振動型ジャイロ方式の唯一の 弱点は、周りの微細な環境ノイズに弱いことである. 本システムについても構造上からノイズ環境による 影響を避けることができないため、ノイズによる信 号劣化の補正と温度変化等のドリフト補正処理が必 要となる 5. また、システム全体を小型化して、場 所に拘らず設置を可能にすることも解決すべきテー マの1つである。

小型化例として仮に振動子本体の小型化を考える と,振動体の剛性や筐体の共振変化の影響によりバ ランスが変わることから応答範囲も変化する. したがって,正常応答を得るためには,ジャイロ本体が振動範囲内で動作するよう,対象目標に対し適切な大きさに加工して組み込むことが必要である.

本研究では、これまでの結果を踏まえて新たなシステムを設計し、ジャイロシステム全体を小型一体化することができたので報告する.

#### 2. 実験方法

#### 2. 1 新型基板の開発

図1に開発した小型ジャイロ基板を示す.前回作成のプロトタイプ基板 40では、シミュレーションモデルとの比較を行っている. 開発した新型基板は当初、名刺大サイズを目標としていたが、その後の基板層や配置配線の見直し検討結果により、さらに小型化が可能となり最終的には約 70×52(mm)となった

図1 新型ジャイロ基板

#### \* 電子·機械研究課

#### 2. 2 部品の実装

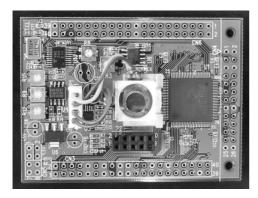

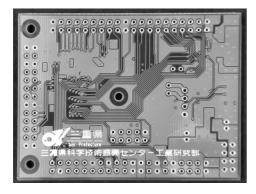

図 2 はジャイロ本体(中央)と周辺部品素子を実装した基板で、図 3 は同基板の裏面を示す.

図2 部品実装状態(真上から)

図3 基板裏面

## 2. 3 集積素子による小型化の実現

小型化が可能となった主な理由として,抵抗コンデンサなどの受動素子類を可能な限りチップ部品に置き換えたことと,PLD(Programmable Logic Device)集積素子の利用によりジャイロからの応答を受ける論理回路ブロックを構築することが可能となったことで,従来の複数 IC(Integrated Circuit)を用いた部分を大幅に縮小できたことである.当初はコストを考え2層基板を目標としていた.しかし,チップ部品の高密度な配置影響とジャイロを中央に配置する必要から,図3のように配線都合上それを避けるように複数本回り込むため,想像以上に部品配置が困難となった.また,同一基板の表裏での電源ラインやグランド配線が複雑に交差するなど,物理結線も限界であったため4層設計となった.

## 2. 4 回路分離によるノイズ低減

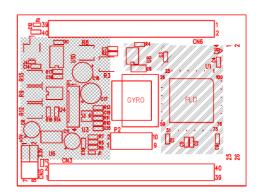

ドライブ周波数は数百 Hz で演算周波数は数十 MHz と 1000 倍以上の差があり、また同一基板上に アナログ信号とデジタル信号が混在することから互

いの不要ノイズ信号の影響を避けるため、図4のように左右の網掛け部分でアナログ、デジタルそれぞれの回路を分離している。同様な理由で、電源層および GND 層は中間層に位置することで放射妨害波の原因となる EMI 対策につながる。さらに、図5は基板のトップ層と電源内層の2層について重ねて見た様子である。PLDの動作電圧範囲は1.8Vから3.3Vで、回路内部には2つのバンクメモリを持つため異なる電源同士が共存可能である。図中の細白線のブロック区画は、それぞれが独立したデジタル・アナログ領域を示している。この回路の分離により、高速クロック動作のデジタル処理部と低速アナログ駆動が混在しているために生ずる互いの影響を避けるため回路的に分離していることと、電源と GNDラインのインピーダンスを下げることができる.

## 2. 5 基板周辺

基板の外周付近には内部信号チェックのためのコネクタ端子群を設けている.これは別装置へのインターフェースとしても利用可能なように100mil(2.54mm)のビア径を配置している.

演算の中心となる PLD の主要信号ピンは周辺コネクタへ接続されており、ピンに対するトライステート入出力など属性変更が可能である.

図4 アナログ-デジタル配置(網かけ)

図5 動作を考慮した内層配線

また,ジャイロ本体近くの 10 ピンモールドコネクタは,PLD に回路構造を書き込むための専用コネクタである.多くの端子類は開発する上で便宜上必要であるが,外部との通信は必要最小限でよいため,用途によっては有効面積をさらに小さくすることも可能である.

#### 3. 結果と考察

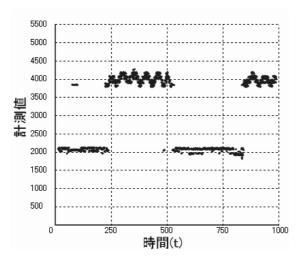

図6は、本ジャイロシステムの独自開発ソフトによる計測結果である. 横軸は時間で、縦軸は振れ幅の大きさを表す. 図7は波形部を拡大表示したものである。波形全体としてはデジタル的な矩形波を成しているが、これはパルスモーターを使った回転計測のため、回転テーブルの回転、ストップを繰り返していることを意味している. 波形の下面はストップ状態での出力値であり、これが安定状態での動作基準値となる. 波形上面は回転時の応答波形である. 途中ギザギザした山状の細かい波が見られるが、こ

図 6 ジャイロ応答の様子

図 7 応答波形拡大

れは回転時のジャイロ中心軸の微妙なブレや回転台 からの共振振動に伴うものと考えられる.

#### 4. まとめ

本研究では、独自開発の二次元振動型ジャイロ本体を1枚のプリント基板上にシステムとして構築し、周辺回路と一体化した新たなシステム開発を行った. その結果として、以下の知見を得ることができた.

- (1)集積回路デバイスおよびチップ素子の利用により高密度な設計が可能となり、目標としていたシステムの小型化が実現できた.

- (2) デジタルとアナログ回路混在によるノイズ影響を考慮した開発ができた.

- (3) 動作表示システムを完成することができた. また,このシステム開発では開発途中で不慮のハードウェアトラブルによる大量のデータ破損が発生し,そのため開発が大幅に遅れたことにより,全体を評価するまでに至らなかった.今後の課題としては,①本システムを利用できる分野の確立と適用アプリケーションの設定,②正常動作時における動作検証および性能評価,が挙げられる.

### 謝辞

これまでの研究でジャイロ振動子開発や特許出願 等でお世話になったベンチャーフォーラム三重様に はこの場を借りて感謝いたします.

#### 参考文献

- 上田知章ほか: "加速度センサ角速度センサのしくみ". DesignWave, p70-71(2007)

- 2) 三重県ほか: "ジャイロ装置". 特開 2005-147978

- 3) 小磯賢智ほか: "二次元振動型マイクロジャイロの開発". 三重県科学技術振興センター工業研究部研究報告, 28, p68-72(2004)

- 4) 小磯賢智: "ジャイロ駆動基板の設計と評価". 三重県科学技術振興センター工業研究部研究報告,31,p47-49(2007)

- 5) 坂本修ほか: "ジャイロ活用技術入門". 工業調査会, p40-42(2002)

(本研究は法人県民税の超過課税を財源としています)